HMP vs. DSP Tradeoffs

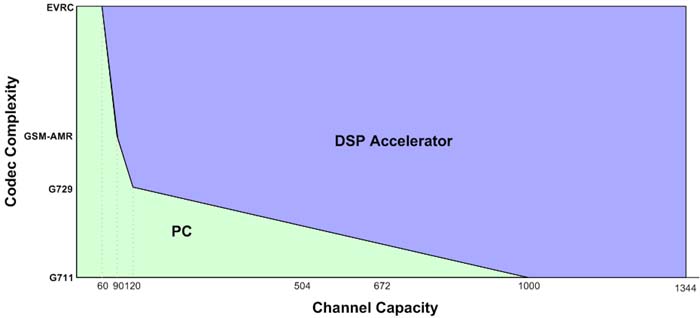

At low channel capacities, the HMP model is effective. As channel capacities

increase, tradeoffs often lead to adding a "DSP accelerator" -- some type of add-in

hardware that substantially increases the capacity of each server. When considering

the "cross over point" at which to scale an HMP platform with a hardware add-on, there

are some useful tradeoffs to keep in mind:

1) Channel Capacity. PC/server platforms have limited video and

voice processing capability. As channel capacities increase, a

cross-over region exists where a choice must be made to either

add more servers or use a DSP accelerator. The cross-over point

is reached sooner depending on the nature of the processing -- for

example, for VoIP impacting factors include the type of voice

codec (e.g. G729, G723, GSM-AMR, EVRC, etc), length of echo

cancellation tail (if needed), and voice quality monitoring (also

if needed).

Below is a curve showing HMP vs. DSP cross-over regions for a VoIP

application, with codec processing complexity on the vertical axis

and channel capacity on the horizontal axis.

The above graph shows HMP-to-DSP crossover for an approximate 3 GHz,

dual Xeon machine.

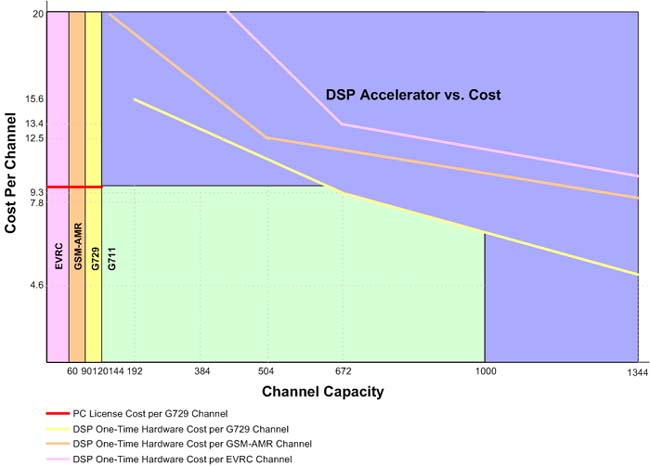

2) Per Channel Cost. At low channel capacities, HMP is far more

cost-effective than DSP. For simple G711 VoIP processing, a DSP

accelerator is not required until the number of channels hits a limit

in the 500 to 1500 channel range, reducing cost per channel to "zero"

if one assumes the PC platform has to be there anyway and is an

inherent cost. But for more complex processing -- or for algorithms

which have significant associated licensing cost -- the cost per

channel can be high.

The graph below gives some idea of typical cost per channel figures for

a DSP solution.

The above graph assumes the cost of the first HMP server itself is

"free"; i.e. the server has to be there anyway to act as a host

platform, and assumes about a $10/channel cost for HMP server

licensing cost for "complex" codecs such as G729, GSM-AMR, etc.

3) IP rights cost must be considered. For example, when a VoIP application requires

100 or more G729 or EVRC channels on an HMP platform, who pays the $1000+ per system

royalty cost? DSPs typically embed IP rights cost within the individual chip cost.

Semiconductor suppliers like Texas Instruments often possess leverage to make

favorable IP licensing deals due to their patent portfolio and cross-licensing

options. How many voice and video codec patents does Intel have compared to TI,

Qualcomm, etc? A quiet submarine is not achieved without practicing for decades.

Intel has not done that; the DSP vendors have.

4) Power Consumption. Power consumption and "system wide complexity" costs rise exponentially with HMP servers. Doubling the number of HMP servers more than doubles "latent costs" such

as power consumption because more than half the electricity cost of an HMP server is

wasted in voice and video applications. As the number of HMP servers increases, more electricity is wasted, both in terms of duplicated functions

and in terms of cooling. Likewise, maintenance cost increases

and MTBF decreases with more cabling, more fans, more power cords, etc. Foreseeable Future

Will more powerful CPUs ever displace DSPs? A simple way to look at this is that

Intel/AMD x86 processors -- in order to provide legacy software support and make

their host systems standardized and easy to use -- must contain millions of

transistors to support Windows and Linux motherboards. More than 80% of these

transistors are wasted when the x86 is asked to perform voice and video processing.

This is the "Intel penalty" for monopolizing the PC/server motherboard market. The

conclusion is straightforward: for the foreseeable future, DSP and FPGA vendors will

continue to exploit this inefficiency, and DSP hardware acceleration will continue to

play a key role in scalable HMP platforms.

Multi-Core VoIP

On a single half-size PCI VoIP card Signalogic has been able to place 72 cores, 600 MHz

each, with total power consumption of only 23 W; with no heatsinks required. In terms of

raw number of cores, the closest x86 solution is a Tyan "Super PC" with 40

cores. In terms of power consumption, there is no x86 solution remotely

comparable.