FFT R&D Project

Overview

Signalogic's FFT R&D project explores the use of CIM accelerators combined with industry standard servers for radar, sonar, and ultrasound (e.g. sonagram) applications. CIM

technology converts industry standard servers into HPC / supercomputing servers, creating inexpensive, easy-to-use platforms for signal processing applications. 32-core

and 64-core CIM PCIe accelerator cards leverage standard programming and development tools, including:

- Linux programming environment

- Open source software

- Intel DPDK, providing a high-throughput, low-latency data plane path between x86 cores and CIM cores

CIM® accelerator cards are thin, light weight, and have low power consumption. For example, three (3) 32-core cards can be inserted

on a single riser in a 2U industry standard server and not exceed the riser power consumption limit of 150 W. A 1U server can be configured

for as many as 256 CIM accelerator cores, and a 2U server for as many as 384 cores.

CIM® accelerator cards contain direct 1 GbE to 10 GbE network connections for high throughput and low latency signal processing,

including virtualized systems.

CIM technology targets

HPC applications in general, providing a low SWaP (size, weight, and power

consumption) alternative to GPUs. Signal processing applications are a subset of HPC applications supported by CIM.

GPU Comparison

CIM cores are high performance, SIMD CPU cores, capable of running C/C++ code that would typically run on x86 cores. A core can optionally run an RTOS and typical associated functions,

such as multithreading, TCP/IP/UDP stacks, Ethernet driver, and drivers for other high-speed peripheral interfaces, such as SRIO and HyperLink. CIM and GPU cores are on a similar

performance/Watt curve (approximately 12 GFlop/Watt, doubling every 18 months), but unlike GPU cores, CIM cores have reduced size and weight (weight associated with infrastructure required

for cooling), making them more suitable for low SWaP (size, weight, and power consumption) applications. Some examples of SWaP constrained applications include:

- Limited server rackspace

- Fixed electric capacity or budget for cooling

- Remote vehicles (drones, satellites, oil & gas exploration trucks, etc)

CIM accelerator cards are targeted at both servers and embedded systems such as shown

here.

HP DL380p 2U server with CIM accelerator installed. Up to six (6) accelerators

HP DL380p 2U server with CIM accelerator installed. Up to six (6) accelerators

can be installed in a 2U server with DPDK interface

|

|

CIM accelerator installed on middle riser and interfaced to

CIM accelerator installed on middle riser and interfaced to

eight (8) data plane x86 cores

|

FFT Functions

Below is a list of signal processing functions currently being parallelized and/or optimized:

Serial FFT

Parallel FFT

Matched Filtering

Convolution

Software Architecture

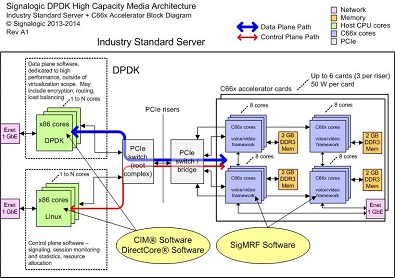

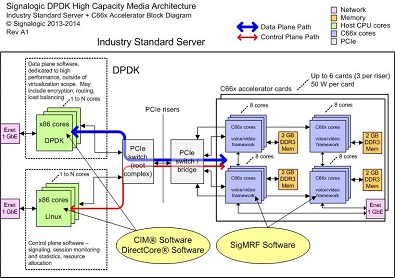

The block diagram below shows a high-throughput, low latency "data plane path" (blue line) between x86 cores and data plane signal processing cores. In this example, control plane

processing is handled by x86 cores running Linux, and control plane related coordination follows the "control plane path" (red line). If the machine is virtualized, data plane

processing -- including Ethernet I/O on the accelerator cards -- would not be visible to the VM.

|

|

DPDK + Accelerator Software Architecture

|

R&D Partner Participation

General Rules

- Participants must be pre-approved under agreement between Signalogic engineering management and an authorized academic supervisor

- You may publish your results with first authorship

- All source code remains the property of Signalogic

Remote Access