Home > Technology & Applications > Server Data Plane Solution for Media Applications

SigMRF - Data Plane High Capacity Media Solution

- Product Status Note (Merged into SigSRF)

- Overview

- Media Resource Functions (MRF)

- Capacity Figures

- Multicore Hardware Supported

- Software Architecture

Product Status Note

- 1) SigMRF has been merged into SigSRF (Streaming Resource Functions), and the mediaTest online demo ◳ is available. The demo includes (i) packet streaming, both real-time and unlimited rate buffering, with packet re-ordering and packet RFCs, (ii) test and measurement, including codec audio quality and performance, media RFC verification, and transcoding, and (iii) an example application, including source code, showing how to use Pktlib and Voplib APIs

- 2) The EVS codec ◳ is now supported, in addition to codecs listed below

- 3) Documentation with high capacity / load x86 server examples is located at SigSRF Software Documentation ◳

Overview

SigMRF is a data plane high capacity media solution for voice and video applications. SigMRF software allows customers to turn industry standard servers into high capacity media resource servers, providing MRF (Media Resource Functions) for SBC, transcoding, and content delivery applications. Both x86 only and x86 + coCPU™ enabled platforms are supported. x86 only high capacity is based on highly optimized SigSRF shared library modules ◳. High capacity examples, including htop screen caps and CPU usage figures for 500 concurrent fully real-time sessions on a single HP 2U server, are included in SigSRF documentation ◳. For coCPU platforms, coCPU cards include 32-core and 64-core c66x PCIe accelerator cards ◳, usable with or without Intel's DPDK 1. coCPU™ accelerator cards are thin, light weight, and have low power consumption. For example, three (3) 32-core cards can be inserted on a single riser in a 2U industry standard server and not exceed the riser power consumption limit of 150 W. A 1U server can be configured for as many as 256 c66x accelerator cores, and a 2U server for as many as 384 cores. coCPU™ accelerator cards contain direct 1 GbE to 10 GbE network connections for high throughput and low latency media processing, including virtualized systems. coCPU technology targets HPC applications in general, providing a low SWaP (size, weight, and power consumption) alternative to GPUs. SigMRF is a telecom focused subset of HPC applications supported by Signalogic.1 DPDK (Data Plane Development Kit) is a thin RTOS running on x86 cores separate from Linux cores wthin a server, optimized with zero-copy, fast interrupt response time, and other ultra high speed methods. DPDK provides high-throughput, low-latency access between x86 cores and high-speed I/O (such as Ethernet from 1 to 40 GbE) and PCIe I/O such as the coCPU accelerator cards. More information on DPDK is here ◳.

Media Resource Functions (MRF)

Below is a list of media resource functions:Codecs, Wireline

- G.711

- G.729AB

- G.723.1

Codecs, Wireless

- AMR-NB

- GSM-EFR

- GSM-FR

- EVRC-AB/li>

- EVS

Codecs, Wideband

- G.711.1

- AMR-WB (G.722.2)

- EVRC-NW

- G.722

- Opus

- EVS

Audio and Voice Functions

- LEC (Line Echo Canceller), 16 to 128 msec tail

- Enhanced LEC

- Narrowband to/from wideband sampling rate conversion

- G.711 Appendix I

- G.711 Appendix II

Telecom Functions

- AEC (Acoustic Echo Canceller)

- T.38 fax

Media Framework Functions

- Conferencing

- Dynamic Jitter Buffer

- Variable ptime

- RTCP and statistics

- Resource monitoring, CPU usage, memory usage

Packet Processing Functions

- IP/UDP/RTP packet processing and parsing

- High throughput PCIe packet interface to DPDK cores

- Additional high throughput Ethernet packet interface (may be combined with PCIe packet interface)

- IPv4 and IPv6 support

Encryption

- Secure RTP (sRTP, AES-128)

- AES-256

- SHA-256

Capacity Figures

Below is a table giving transcoding capacity figures for a SigC6678 "quad" accelerator card with 32 cores. Some notes about the table:- In the "Encode, Decode, or Both" column, a "B" means both encode and decode (typical transocde situation).

- A nominal framework overhead percentage of 30% is shown. This can vary, for instance higher overhead with heavier echo cancellation load.

- An Excel spreadsheet version of the table is available under NDA, allowing number of cores, overhead percentage, and transcoding combinations to be varied.

| CPU / Accelerator Type | |||||||||

| SigC6678 Accelerator Voice / Video Capacity Copyright © Signalogic 2013-2014 |

x86 1 | coCPU 2 | |||||||

| Number of cores | 16 | 32 | |||||||

| Clock rate (GHz) | 3.00 | 1.25 | |||||||

| Framework overhead (%) | 30% | ||||||||

| Codec(s) | Fps | Encode,

Decode, or Both |

Enc Cores3 | Dec Cores3 | |||||

| V i d e o |

|||||||||

| H.264 720p BP 1 Mbps | 15 | E | 2 | 1 | 18 | ||||

| VP8 720p 1 Mbps | 15 | E | 4 | 1 | 9 | ||||

| MPEG2 720p BP 4 Mbps | 15 | E | 2 | 18 | |||||

| H.264 1080p BP 1 Mbps | 15 | E | 2 | 1 | 18 | ||||

| VP8 1080p 1 Mbps | 15 | E | 4 | 1 | 9 | ||||

| MPEG2 1080p BP 4 Mbps | 15 | E | 2 | 18 | |||||

| H.264 CIF MP 500 kbps | 15 | E | 2 | 1 | 18 | ||||

| H.264 QCIF MP 250 kbps | 15 | E | 1 | 1 | 36 | ||||

| S p e e c h |

G.711 | B | 47458 | ||||||

| AMR-NB | B | 4288 | |||||||

| AMR-WB | B | 1810 | |||||||

| EVRC | B | 2602 | |||||||

| G.722 | B | 8777 | |||||||

| G.722.1 (16 kHz Fs) | B | 10566 | |||||||

| G.723.1A | B | 5773 | |||||||

| G.729AB | B | 5501 | |||||||

| GSM FR | B | 23729 | |||||||

| GSM HR | B | 3900 | |||||||

| iLBC | B | 3230 | |||||||

| 1 Intel Sandy Bridge | |||||||||

| 2 Texas Inst C66x | |||||||||

| 3 Dedicated cores required due to optimized algorithm | |||||||||

Multicore Hardware Supported

Several types of multicore hardware are supported for coCPU acceleration, including:- Advantech 32-core and 64-core PCIe cards (DSPC-8681 and DSPC-8682). Clock rates 1, 1.25, and 1.5 GHz. DDR3 mem amounts 1 and 2 GByte

- Comm Agility 32-core uATCA modules

- Advantech 160-core ATCA boards (8901 board). DDR3 mem amounts 1 and 2 GByte

Software Architecture

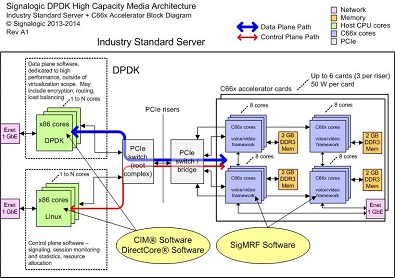

The block diagram below shows a high-throughput, low latency "data plane path" (blue line) between x86 cores and data plane media processing cores. In this example, control plane processing is handled by x86 cores running Linux, and control plane related coordination follows the "control plane path" (red line). If the machine is virtualized, data plane processing -- including Ethernet I/O on the accelerator cards -- would not be visible to the VM.

|

| DPDK + Accelerator Software Architecture |